漢中略陽羌文化生態保護試驗區 羌族建筑的獨特魅力與遺址保護服務

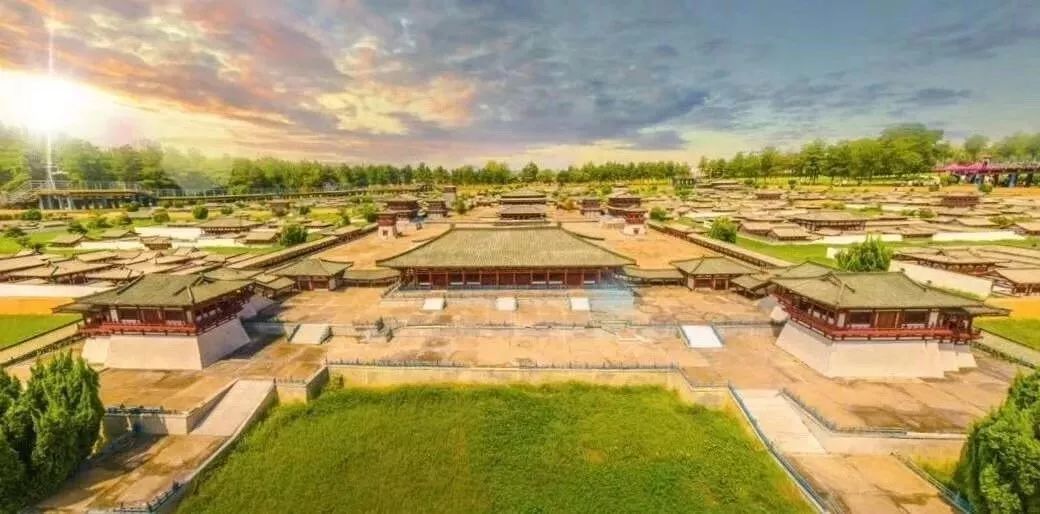

漢中略陽羌文化生態保護試驗區,作為羌族文化的重要傳承地,以其獨特的羌族建筑和系統的文物文化遺址保護服務,吸引了眾多文化愛好者和研究者的目光。這里的建筑不僅是羌族人民智慧的結晶,更是中華民族多元文化的重要組成部分。

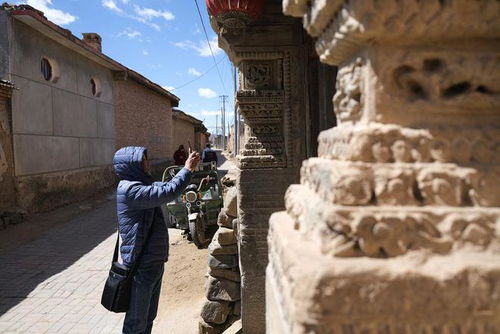

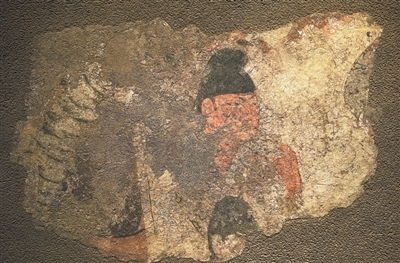

羌族建筑以其獨特的風格和精湛的工藝聞名。在略陽保護試驗區內,傳統的羌族碉樓、石砌民居和木結構建筑隨處可見。這些建筑多依山而建,采用當地豐富的石材和木材,結構堅固,造型古樸。碉樓作為羌族建筑的標志,通常高達數層,不僅用于居住,還具有防御功能。其墻體厚實,窗戶小巧,體現了羌族人民在艱苦自然環境中的生存智慧。民居則多采用石木混合結構,屋頂以石板覆蓋,既防風又防水,與周圍的自然景觀和諧相融。建筑上的雕刻和裝飾,如羊頭、云紋等圖案,蘊含著羌族的圖騰信仰和文化象征,每一處細節都訴說著這個古老民族的歷史與故事。

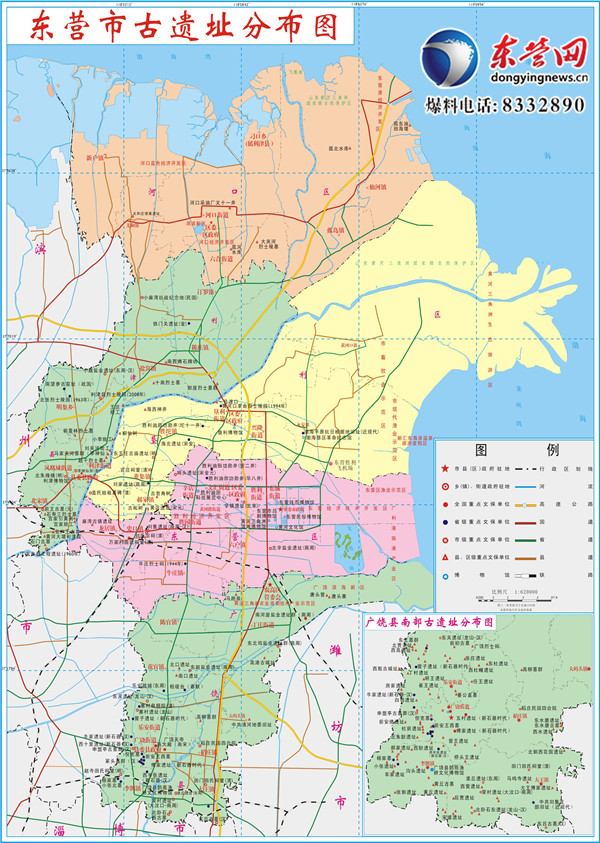

略陽羌文化生態保護試驗區在文物文化遺址保護服務方面做出了顯著努力。為了保護這些珍貴的建筑遺產,當地政府和文化部門采取了一系列措施。通過科學調研和規劃,劃定核心保護區和緩沖區,確保建筑群的原真性和完整性得到維護。加強日常監測和維護,定期對古建筑進行安全檢查,防止自然侵蝕和人為破壞。例如,針對碉樓的結構穩定性,專家團隊會使用現代技術進行檢測,并及時修復裂縫或加固基礎。保護服務還包括對羌族建筑技藝的傳承,通過培訓當地工匠,鼓勵他們使用傳統工藝進行修復和新建,避免文化斷層。

略陽保護區還注重文化遺址的活化利用。在保護的前提下,部分建筑被改造為文化展示館或體驗中心,向游客介紹羌族的歷史、藝術和生活方式。例如,一些石砌民居內設有羌繡、羌笛等非遺項目的展示區,讓參觀者親身體驗羌族文化的魅力。這種保護與旅游相結合的模式,不僅提高了公眾對羌族建筑價值的認識,還為當地社區帶來了經濟收益,促進了文化保護的可持續發展。

值得一提的是,略陽的羌族建筑保護服務還融入了生態理念。由于羌族建筑與自然環境緊密相連,保護工作強調“天人合一”的思想,避免過度開發,保持山水與建筑的和諧。例如,在修復過程中,優先使用環保材料,并盡量減少對周邊植被的干擾。這種生態保護與文化保護并重的做法,使得略陽羌文化生態保護試驗區成為一個生動的文化生態樣本,為其他地區的遺產保護提供了借鑒。

漢中略陽羌文化生態保護試驗區的羌族建筑以其獨特的藝術價值和歷史意義,成為中華文化寶庫中的璀璨明珠。通過系統的文物文化遺址保護服務,這些建筑得以延續生命,繼續講述羌族的故事。隨著保護工作的深入推進,略陽有望成為羌文化研究與傳播的重要基地,讓更多人領略到羌族建筑的特色與魅力,共同守護這份珍貴的文化遺產。

如若轉載,請注明出處:http://www.jaqr.cn/product/73.html

更新時間:2026-03-06 04:06:06