數(shù)字集成電路測(cè)試儀硬件的設(shè)計(jì)與軟件開(kāi)發(fā)

數(shù)字集成電路測(cè)試儀在現(xiàn)代電子工業(yè)中扮演著關(guān)鍵角色,它能夠檢測(cè)芯片的功能、性能和可靠性,確保產(chǎn)品質(zhì)量。本文將分別從硬件設(shè)計(jì)和軟件開(kāi)發(fā)兩個(gè)方面展開(kāi)討論,闡述其設(shè)計(jì)原則、關(guān)鍵技術(shù)和實(shí)現(xiàn)過(guò)程。

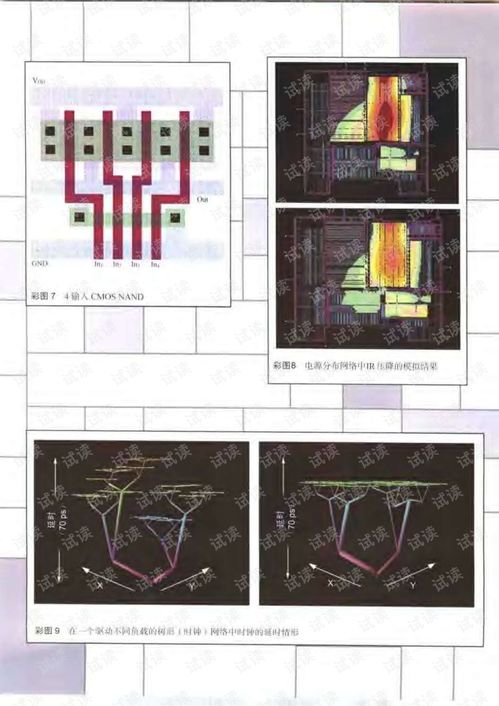

一、數(shù)字集成電路測(cè)試儀硬件設(shè)計(jì)

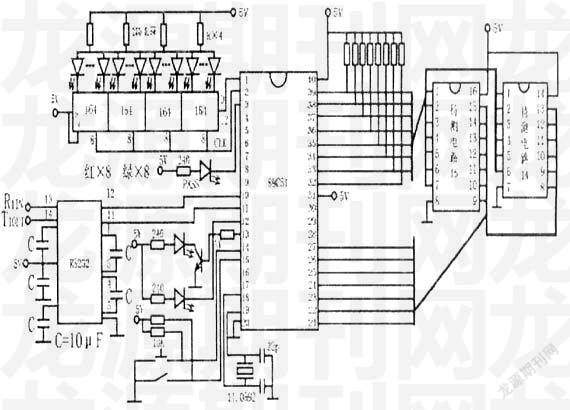

硬件設(shè)計(jì)是數(shù)字集成電路測(cè)試儀的基礎(chǔ),直接決定了測(cè)試的精度、速度和可靠性。其主要組成部分包括:

- 測(cè)試頭與引腳電子系統(tǒng):測(cè)試頭負(fù)責(zé)與待測(cè)芯片(DUT)物理連接,引腳電子系統(tǒng)則通過(guò)驅(qū)動(dòng)器、比較器和負(fù)載電路實(shí)現(xiàn)信號(hào)輸入和輸出。設(shè)計(jì)時(shí)需考慮引腳數(shù)(從幾十到上千)、信號(hào)頻率(可達(dá)GHz級(jí)別)和電壓范圍(如0-5V),同時(shí)采用高速PCB布局和阻抗匹配技術(shù)以減少信號(hào)失真。

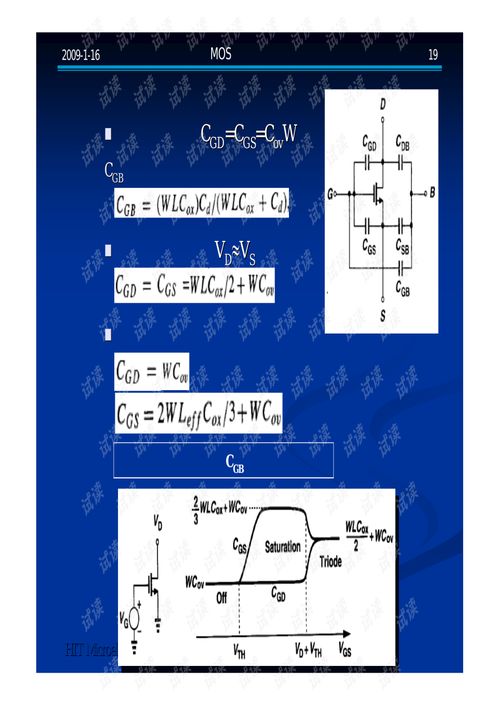

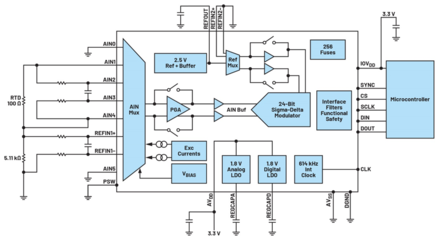

- 定時(shí)與同步系統(tǒng):定時(shí)系統(tǒng)生成精確的時(shí)鐘和時(shí)序信號(hào),確保測(cè)試信號(hào)與芯片操作同步。這通常涉及高精度時(shí)鐘發(fā)生器、延遲線和可編程邏輯器件(如FPGA),以實(shí)現(xiàn)納秒級(jí)的時(shí)間分辨率,并支持多時(shí)鐘域測(cè)試。

- 電源管理系統(tǒng):為待測(cè)芯片和測(cè)試儀自身提供穩(wěn)定電源,包括多路可編程電源、電流監(jiān)測(cè)和過(guò)載保護(hù)電路。設(shè)計(jì)需關(guān)注電源噪聲抑制和動(dòng)態(tài)響應(yīng),例如使用線性穩(wěn)壓器和濾波電路來(lái)保證電壓精度在±1%以內(nèi)。

- 數(shù)據(jù)采集與存儲(chǔ)單元:通過(guò)ADC(模數(shù)轉(zhuǎn)換器)和高速存儲(chǔ)器捕獲測(cè)試結(jié)果,支持實(shí)時(shí)數(shù)據(jù)分析和故障診斷。硬件設(shè)計(jì)中常集成大容量RAM和高速接口(如PCIe),以處理海量測(cè)試數(shù)據(jù)。

- 散熱與機(jī)械結(jié)構(gòu):由于測(cè)試儀在高頻下運(yùn)行會(huì)產(chǎn)生大量熱量,需采用散熱片、風(fēng)扇或液冷系統(tǒng),并結(jié)合堅(jiān)固的機(jī)械外殼,確保長(zhǎng)期穩(wěn)定性和電磁兼容性(EMC)。

硬件設(shè)計(jì)的關(guān)鍵挑戰(zhàn)在于平衡性能與成本,例如通過(guò)模塊化設(shè)計(jì)提高可擴(kuò)展性,并遵循行業(yè)標(biāo)準(zhǔn)(如IEEE 1149.1 JTAG)以增強(qiáng)兼容性。

二、數(shù)字集成電路測(cè)試儀的軟件開(kāi)發(fā)

軟件開(kāi)發(fā)是測(cè)試儀的靈魂,它控制硬件操作、處理測(cè)試數(shù)據(jù)并提供用戶界面。軟件系統(tǒng)通常包括以下層次:

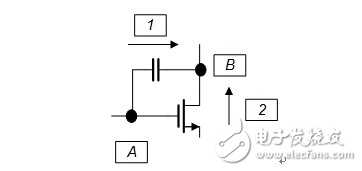

- 底層驅(qū)動(dòng)與固件:直接與硬件交互,實(shí)現(xiàn)信號(hào)生成、數(shù)據(jù)采集和時(shí)序控制。這部分常用C/C++或VHDL/Verilog編寫(xiě),運(yùn)行在FPGA或微控制器上,確保低延遲和高實(shí)時(shí)性。例如,通過(guò)固件優(yōu)化,可將測(cè)試周期縮短至微秒級(jí)。

- 測(cè)試程序開(kāi)發(fā):測(cè)試程序定義了具體的測(cè)試流程,如功能測(cè)試、參數(shù)測(cè)試和邊界掃描。開(kāi)發(fā)語(yǔ)言常采用標(biāo)準(zhǔn)測(cè)試語(yǔ)言(如STIL或ATPG工具),支持向量生成、故障模擬和模式壓縮。關(guān)鍵點(diǎn)包括:

- 向量生成:基于芯片規(guī)格書(shū)創(chuàng)建輸入激勵(lì)和預(yù)期輸出。

- 故障覆蓋分析:使用算法(如Stuck-at或延遲故障模型)確保測(cè)試覆蓋率高(通常>95%)。

- 調(diào)試工具:集成邏輯分析器和仿真環(huán)境,幫助工程師快速定位故障。

- 上層應(yīng)用與用戶界面:提供圖形化界面(GUI),允許用戶配置測(cè)試參數(shù)、監(jiān)控狀態(tài)和查看報(bào)告。開(kāi)發(fā)工具可能包括Python、Java或LabVIEW,強(qiáng)調(diào)易用性和可視化。例如,通過(guò)拖拽式界面設(shè)置測(cè)試序列,并生成PDF或CSV格式的測(cè)試報(bào)告。

- 數(shù)據(jù)分析與云集成:軟件集成數(shù)據(jù)分析和機(jī)器學(xué)習(xí)模塊,用于趨勢(shì)預(yù)測(cè)和智能診斷。現(xiàn)代測(cè)試儀常支持云平臺(tái)連接,實(shí)現(xiàn)遠(yuǎn)程監(jiān)控和大數(shù)據(jù)處理,從而提高測(cè)試效率和可維護(hù)性。

軟件開(kāi)發(fā)需注重模塊化和標(biāo)準(zhǔn)化,例如采用面向?qū)ο笤O(shè)計(jì)(OOP)和API接口,以便與第三方工具(如EDA軟件)集成。安全性和可擴(kuò)展性也是重要考量,如通過(guò)加密通信保護(hù)測(cè)試數(shù)據(jù)。

三、硬件與軟件的協(xié)同設(shè)計(jì)

成功的數(shù)字集成電路測(cè)試儀依賴于硬件與軟件的緊密集成。設(shè)計(jì)過(guò)程中,需進(jìn)行聯(lián)合仿真和驗(yàn)證,例如使用虛擬原型工具在軟件中模擬硬件行為,減少開(kāi)發(fā)周期。同時(shí),標(biāo)準(zhǔn)化接口(如PXI或LXI)促進(jìn)了模塊化升級(jí)和維護(hù)。

數(shù)字集成電路測(cè)試儀的設(shè)計(jì)是一個(gè)多學(xué)科工程,硬件提供精準(zhǔn)的物理基礎(chǔ),軟件賦予智能控制能力。隨著AI和5G技術(shù)的發(fā)展,未來(lái)測(cè)試儀將更注重高速、高密度和智能化,設(shè)計(jì)者需持續(xù)創(chuàng)新以應(yīng)對(duì)復(fù)雜芯片的挑戰(zhàn)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.jaqr.cn/product/16.html

更新時(shí)間:2026-01-23 23:25:39