集成電路設(shè)計 微縮世界中的智慧與挑戰(zhàn)

在科技飛速發(fā)展的今天,集成電路(IC)已成為現(xiàn)代電子產(chǎn)品的核心,從智能手機、電腦到汽車、醫(yī)療設(shè)備,無處不在。集成電路設(shè)計,作為這一核心的創(chuàng)造過程,是一門融合了電子工程、物理學、計算機科學和材料科學的復雜藝術(shù)與科學。它不僅僅是繪制電路圖,更是一場在微米甚至納米尺度上進行的精密編排,旨在實現(xiàn)功能、性能、功耗和成本的最優(yōu)平衡。

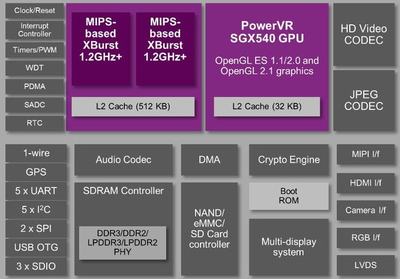

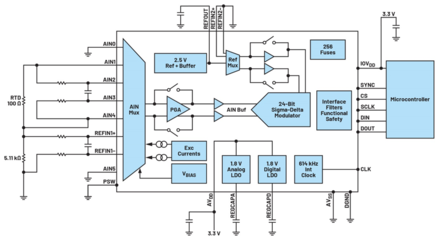

集成電路設(shè)計的旅程始于系統(tǒng)架構(gòu)定義。設(shè)計團隊首先需要明確芯片的功能需求,例如處理速度、存儲容量和能效指標。這一階段如同繪制建筑的藍圖,決定了芯片的整體框架和模塊劃分。進入邏輯設(shè)計階段,工程師使用硬件描述語言(如Verilog或VHDL)將功能轉(zhuǎn)化為數(shù)字電路模型,通過仿真驗證其正確性。這一步確保了芯片的邏輯行為符合預期,為后續(xù)實現(xiàn)奠定基礎(chǔ)。

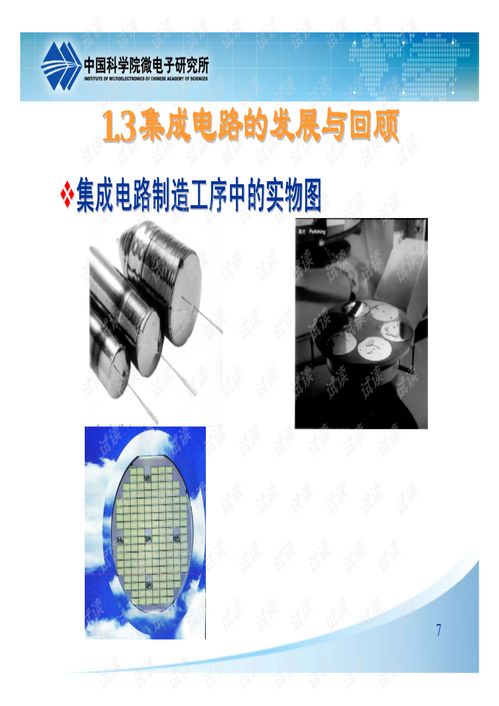

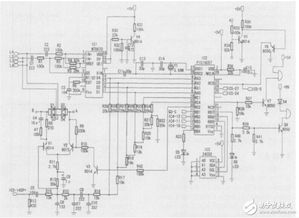

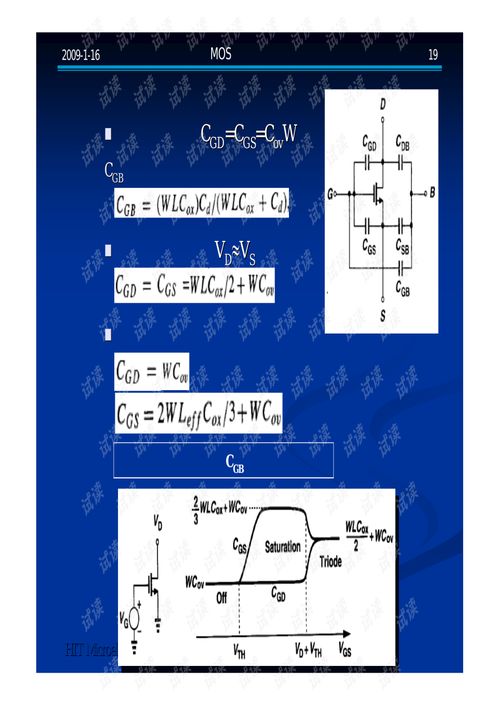

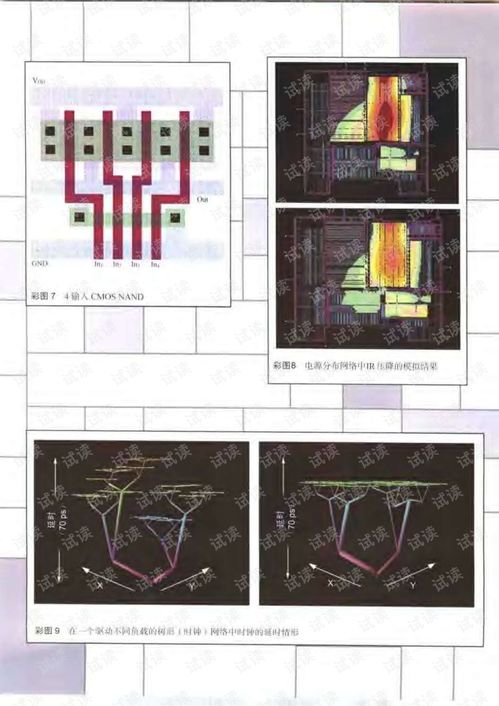

接下來是物理設(shè)計,這是將邏輯模型轉(zhuǎn)化為實際布局的關(guān)鍵步驟。工程師需要將電路元件(如晶體管、電阻和電容)放置在硅片上,并用金屬線連接它們,形成復雜的互連網(wǎng)絡(luò)。這個過程必須考慮諸多因素:如何最小化面積以降低成本,如何優(yōu)化布線以減少信號延遲和功耗,以及如何應對制造過程中的物理限制(如熱效應和電磁干擾)。隨著工藝節(jié)點不斷微縮至7納米、5納米甚至更小,設(shè)計挑戰(zhàn)日益加劇,量子效應和制造變異等問題凸顯,要求設(shè)計工具和方法持續(xù)創(chuàng)新。

驗證與測試貫穿整個設(shè)計流程。在芯片制造前,團隊通過形式驗證、時序分析和物理驗證等手段,確保設(shè)計無誤;流片后,還需進行硅片測試,排查缺陷。據(jù)統(tǒng)計,一次流片成本可高達數(shù)百萬美元,因此“首次成功”至關(guān)重要,推動了電子設(shè)計自動化(EDA)工具的快速發(fā)展,它們提供從合成到布局的智能解決方案,幫助工程師高效應對復雜性。

集成電路設(shè)計正面臨新的機遇與挑戰(zhàn)。人工智能和物聯(lián)網(wǎng)的興起,催生了對專用芯片(如AI加速器和低功耗傳感器)的需求,推動設(shè)計向異構(gòu)集成和三維堆疊演進。全球供應鏈問題和摩爾定律的放緩,促使行業(yè)探索新材料(如碳納米管)和新型架構(gòu)(如神經(jīng)形態(tài)計算)。在中國,集成電路設(shè)計作為國家戰(zhàn)略重點,正迎來政策支持和市場增長,本土企業(yè)如華為海思和紫光展銳在移動通信和物聯(lián)網(wǎng)領(lǐng)域嶄露頭角,但仍在高端工藝和EDA工具方面面臨追趕壓力。

集成電路設(shè)計是連接創(chuàng)新與現(xiàn)實的橋梁,它不僅是技術(shù)進步的引擎,更是國家競爭力的體現(xiàn)。在微縮的世界里,每一顆芯片都凝聚著無數(shù)工程師的智慧,驅(qū)動著我們邁向更智能、更互聯(lián)的未來。隨著技術(shù)不斷突破,這場設(shè)計之旅將繼續(xù)書寫電子時代的新篇章。

如若轉(zhuǎn)載,請注明出處:http://www.jaqr.cn/product/46.html

更新時間:2026-01-21 23:17:38