基于14443A協(xié)議的無源電子標(biāo)簽數(shù)字集成電路設(shè)計

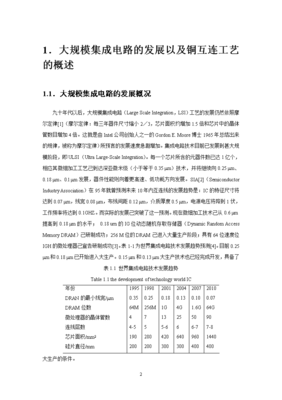

隨著物聯(lián)網(wǎng)和智能識別技術(shù)的快速發(fā)展,無源電子標(biāo)簽作為一種低成本、高效率的識別解決方案,被廣泛應(yīng)用于門禁、物流管理和移動支付等領(lǐng)域。其中,基于ISO/IEC 14443A協(xié)議的無源電子標(biāo)簽因其高兼容性和可靠性備受青睞。本文將探討基于14443A協(xié)議的無源電子標(biāo)簽數(shù)字集成電路設(shè)計的關(guān)鍵方面,包括協(xié)議概述、系統(tǒng)架構(gòu)、模塊設(shè)計以及設(shè)計挑戰(zhàn)與優(yōu)化策略。

14443A協(xié)議是近場通信(NFC)標(biāo)準(zhǔn)的一部分,定義了非接觸式智能卡和讀卡器之間的通信規(guī)范。它采用13.56MHz載波頻率,支持?jǐn)?shù)據(jù)傳輸速率最高達(dá)848kbps。協(xié)議包括初始化、防碰撞機(jī)制和數(shù)據(jù)交換三個階段,確保多標(biāo)簽環(huán)境下的穩(wěn)定通信。在設(shè)計數(shù)字集成電路時,必須嚴(yán)格遵循這些協(xié)議要求,以實現(xiàn)與標(biāo)準(zhǔn)讀卡器的互操作性。

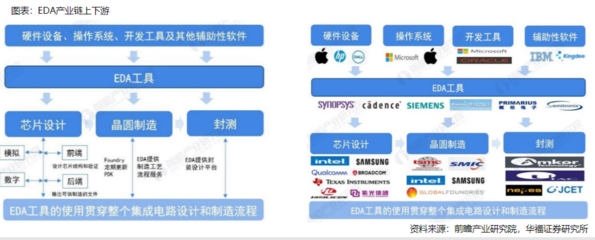

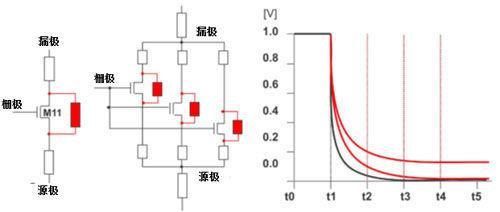

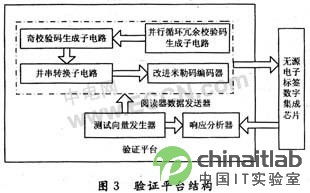

無源電子標(biāo)簽的數(shù)字集成電路設(shè)計通常采用低功耗CMOS工藝,以最大化能量采集效率。系統(tǒng)架構(gòu)包括射頻前端、數(shù)字基帶處理單元和存儲模塊。射頻前端負(fù)責(zé)從讀卡器發(fā)射的電磁場中采集能量和解調(diào)信號,而數(shù)字基帶處理單元則實現(xiàn)協(xié)議邏輯,包括命令解析、防碰撞算法和數(shù)據(jù)加密。存儲模塊通常使用EEPROM或FRAM,用于存儲唯一標(biāo)識符(UID)和用戶數(shù)據(jù)。

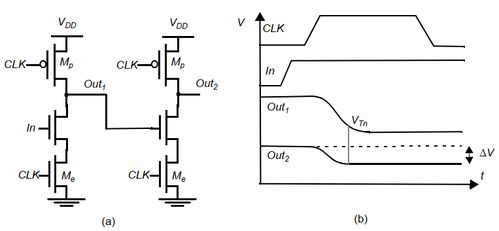

在模塊設(shè)計中,防碰撞機(jī)制是關(guān)鍵部分。14443A協(xié)議采用基于時隙的防碰撞算法,數(shù)字電路需要實現(xiàn)高效的時隙管理和響應(yīng)邏輯,以避免多標(biāo)簽沖突。功耗優(yōu)化是設(shè)計中的核心挑戰(zhàn)。由于標(biāo)簽依賴讀卡器供能,電路設(shè)計需最小化靜態(tài)和動態(tài)功耗。例如,采用時鐘門控、電源門控和低電壓設(shè)計技術(shù),可以顯著降低功耗,同時保持性能。仿真和驗證流程包括使用HDL(如Verilog或VHDL)進(jìn)行建模,并通過FPGA原型測試確保功能正確性。

設(shè)計過程中面臨諸多挑戰(zhàn),如電磁干擾(EMI)的抑制、面積約束和成本控制。優(yōu)化策略包括集成模擬-數(shù)字混合信號設(shè)計、采用先進(jìn)工藝節(jié)點以減小芯片尺寸,以及實施冗余錯誤檢測機(jī)制提高可靠性。未來,隨著人工智能和邊緣計算的興起,無源電子標(biāo)簽可能集成更多智能功能,如傳感器接口和自適應(yīng)通信協(xié)議,這對集成電路設(shè)計提出了更高要求。

基于14443A協(xié)議的無源電子標(biāo)簽數(shù)字集成電路設(shè)計是一個多學(xué)科交叉的領(lǐng)域,涉及通信協(xié)議、低功耗設(shè)計和信號處理。通過精細(xì)的架構(gòu)規(guī)劃和優(yōu)化,可以實現(xiàn)高性能、低成本的標(biāo)簽解決方案,推動物聯(lián)網(wǎng)應(yīng)用的普及。未來研究可聚焦于能效提升和多協(xié)議兼容性,以適應(yīng)不斷變化的市場需求。

如若轉(zhuǎn)載,請注明出處:http://www.jaqr.cn/product/10.html

更新時間:2026-01-23 00:17:50